サムスンは1c DRAMを採用したHBM4の量産準備を進め、High-NA EUV導入で微細化とコスト競争力を強化。HBM歩留まりは積層やTSV工程に課題を抱えるが、DRAM品質向上が間接的に改善を後押しする。さらにSK hynixと共に最大30%の価格引き上げを進め、AI需要拡大を背景にメモリ市場で存在感を高める。

サムスン、1c DRAMとEUV投資でHBM4加速

HBM4と1c DRAMの採用

サムスンは次世代高帯域幅メモリ(HBM4)の量産準備を進めており、その基盤技術として1c DRAMプロセスを導入している。1c DRAMは従来世代(1b)よりも微細化が進み、セル密度の向上と消費電力の削減を両立。AIやHPC用途で求められる大容量・高帯域幅・低消費電力を実現する鍵となる。

あわせて読みたい:(NANDフラッシュメモリ)サムスン第7世代176層・第8世代236層・第9世代321層V-NAND進化とSSD市場回復、1000層時代へのロードマップ

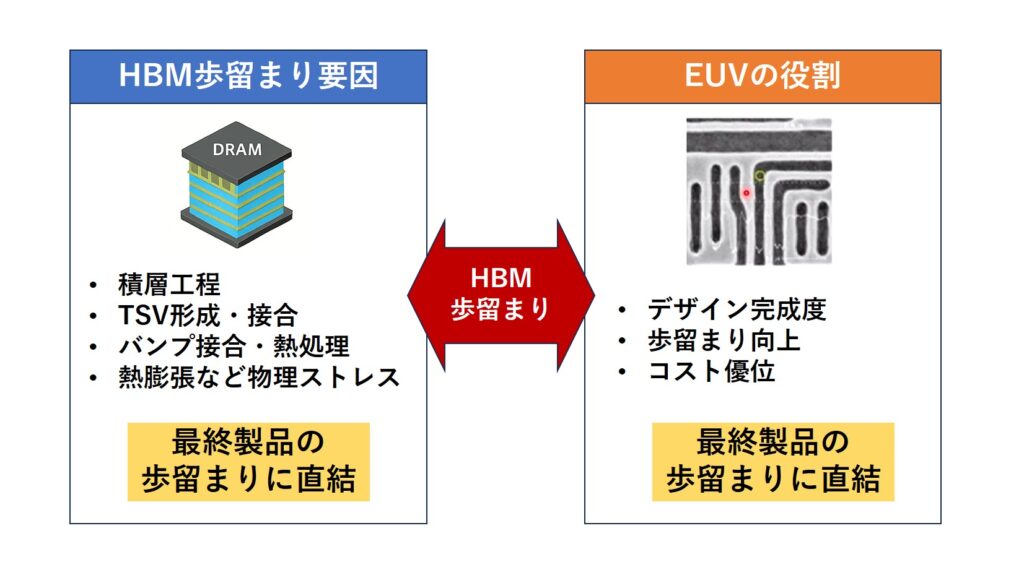

HBM歩留まりの課題

現時点での1c DRAMベースHBM4の歩留まりは約50%と報じられており、競合のSK hynixやマイクロンに比べて劣勢とされる。HBMの歩留まりを決めるのは、積層工程・TSV形成・接合技術・熱処理といったパッケージング要因が大きい。したがって、DRAMチップ単体の品質向上がHBM全体の歩留まり改善に直結する。

EUVの優位性とDRAM投資加速

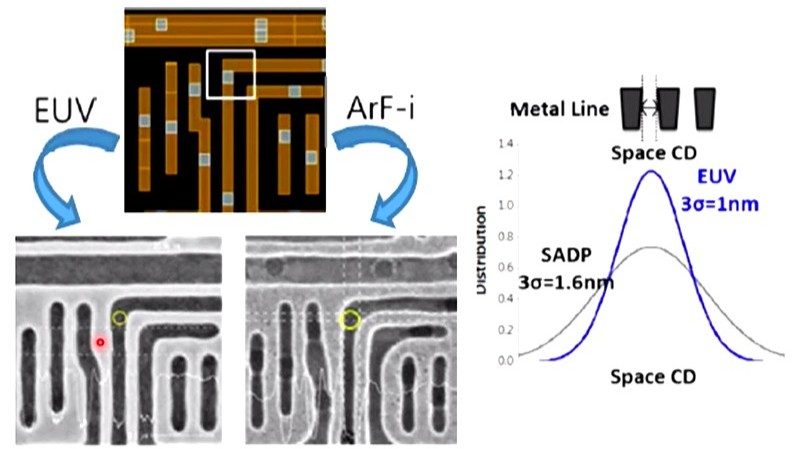

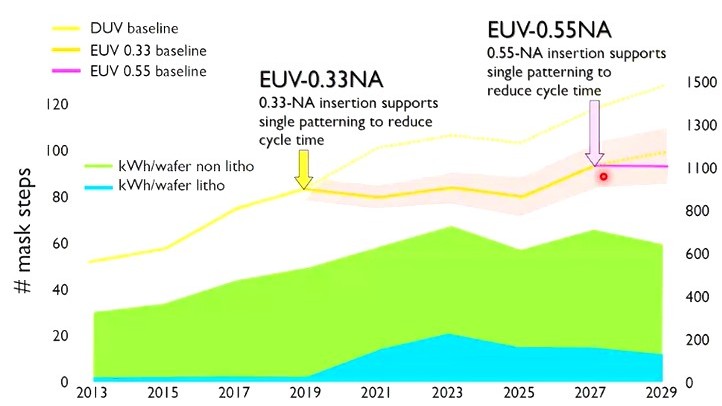

サムスンはASMLのHigh-NA EUV露光装置を2台導入予定であり、これを2nmロジックとDRAM製造に活用する。EUVの導入は以下の点でDRAM投資の加速と歩留まり改善に結び付く。

- デザイン完成度の高さ

単一露光で微細パターンを形成でき、パターン忠実度が高い。設計ルール縮小(1b→1c)を可能にし、セル密度を向上。 - 歩留まりの向上

多重パターニングを不要にすることで欠陥源を削減。寸法ばらつきが小さく、DRAMチップ単体の良品率が向上。結果としてHBM積層時の総合歩留まり改善に寄与。 - コスト優位性

マスク数と工程数を削減し、製造サイクルを短縮。初期投資は大きいが、量産段階では歩留まり改善+工程削減により総コストを抑制できる。

価格戦略と市場動向

一方で、業界全体では最大30%の価格引き上げが進んでいる。サムスンとSK hynixは長期供給契約を背景に価格を押し上げ、AIサーバー需要の急増による供給逼迫が価格上昇を後押ししている。TrendForceによれば、2026年にかけてメモリ価格は高止まりする可能性が高い。

あわせて読みたい:👉半導体記事一覧

DRAM世代の位置づけ(注釈)

DRAMの「1x〜1c」世代はすべて10nmクラスに属するが、各社は正確なnm値を公表していない。業界推定値は以下の通り。

| 世代 | 推定デザインルール | 特徴 |

|---|---|---|

| 1x | 約18nm前後 | DDR4後期、初期DDR5に採用 |

| 1y | 約15〜16nm | DDR5普及期 |

| 1z | 約14nm | HBM2E/DDR5強化 |

| 1α | 約13〜14nm | EUV部分導入、DDR5/LPDDR5 |

| 1β | 約12nm台 | EUV適用拡大、HBM3Eなど |

| 1c | 約10〜11nm台 | EUV本格導入、HBM4/DDR5/LPDDR6/GDDR7 |

総括

サムスンは1c DRAMとEUV投資を軸に、HBM4での競争力強化を狙っている。HBM歩留まりは依然として積層工程に左右されるが、EUVによるDRAMチップ品質の底上げとコスト削減効果は、最終的なHBM量産の安定化に不可欠だ。さらに、業界全体の価格上昇局面がサムスンに追い風となり、技術課題の克服・投資成果の実現・価格戦略の三本柱が今後の成否を決定づけるだろう。

コメント