SEMICON Japan最終日で明らかになった半導体の未来を詳しくレポート。3次元集積が主役となる次世代ロジックのロードマップ、CMOS 2.0が示す異種統合の方向性、Intelが採用するBSPDNを支えるウェーハ接合技術、キオクシアが提案するOCTRAMによるDRAM革新まで、先端半導体技術の最新動向を解説します。

【SEMICON Japan 2025 最終日レポート】

3次元集積が切り拓く半導体の新時代 ― 先端デバイス・プロセスセッションまとめ

12月17日から3日間にわたり開催された SEMICON Japan 2025 が盛況のうちに閉幕した。会場には連日多くの来場者が訪れ、日本の半導体産業に対する期待の高さを改めて感じさせるイベントとなった。

最終日の注目プログラム「先端デバイス・プロセスセッション」では、3次元集積技術を中心に、先端半導体の最新動向と未来展望が語られた。本記事では、その内容をわかりやすくまとめる。

あわせて読みたい:

・SEMICON Japan 2025開幕|TSMC江本裕氏が語る製造革新と歩留まり改善、顧客の顧客を見据えた重要メッセージ

・SEMICON Japan 2025 2日目レポート|ラピダス赤堀氏と日立ハイテクLee氏が語る検査・計測技術の未来

3次元構造が主役へ:先端ロジックチップのロードマップ(imec 堀口直人氏)

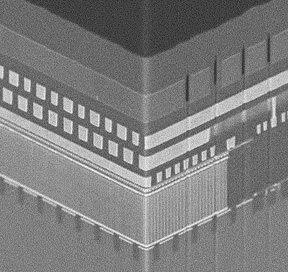

セッション冒頭では、imecの堀口氏が ロジックデバイスの多段集積化 をテーマに講演した。ナノシートFETやロジック+メモリの積層構造など、すでに量産レベルで3次元化が進んでいる現状が紹介され、今後の焦点は次の技術へ移ると説明した。

- CFET(Complementary FET):NMOSとPMOSの垂直積層

- Backside engineering:裏面配線・裏面電源供給

- specialized tiers による機能分離と再統合

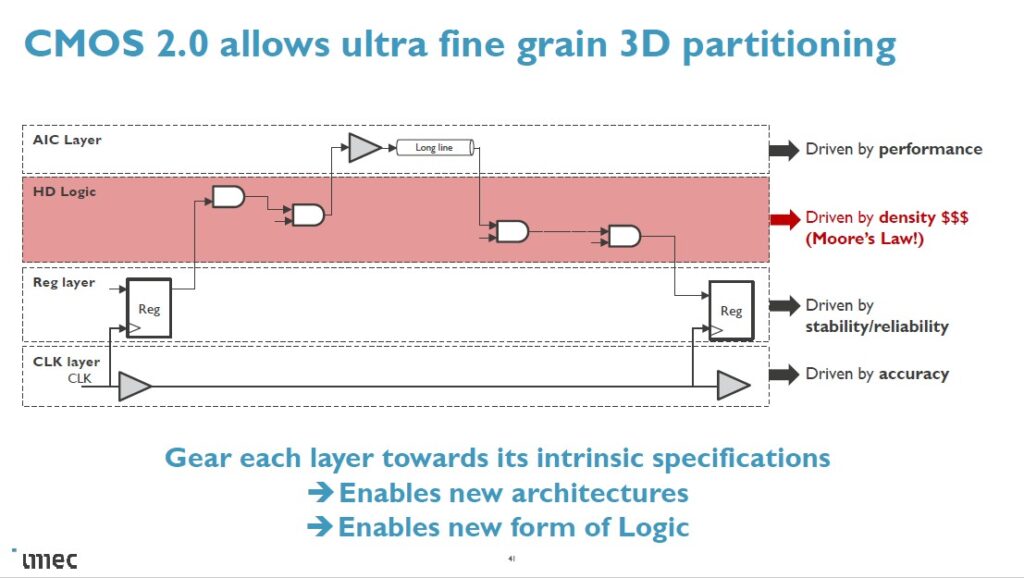

従来の微細化(CMOS 1.0)は、High-NA EUV や Nanosheet FET によって延命されてきたが、歩留まりやPPAの維持が限界に近づいている。そこで imec が示す次のステージが CMOS 2.0 だ。

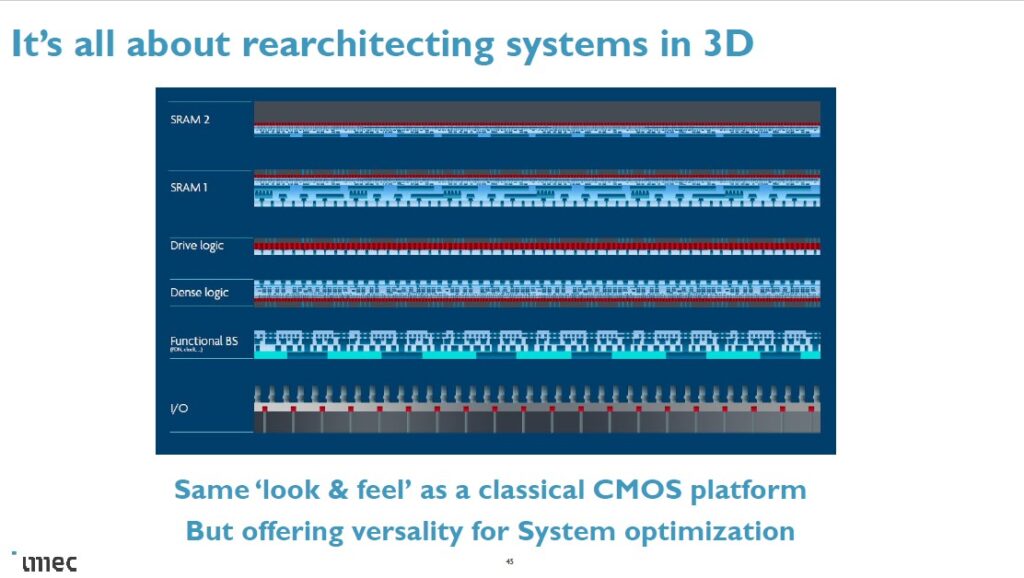

CMOS 2.0 = specialized tiers × backside processing × hybrid bonding

システム機能を階層化し、裏面処理とハイブリッドボンディングで再統合することで、汎用CMOSを異種統合プラットフォームへ進化させる。

「3次元集積がスケーリングを再定義する」時代が本格的に始まろうとしている。

BSPDNを支えるウェーハ接合技術(東京エレクトロン九州 近藤良弘氏)

続いて登壇した東京エレクトロン九州の近藤氏は、Intelが18A世代から採用した BSPDN(Back-Side Power Delivery Network;裏面配線) を支えるウェーハ接合技術について解説した。

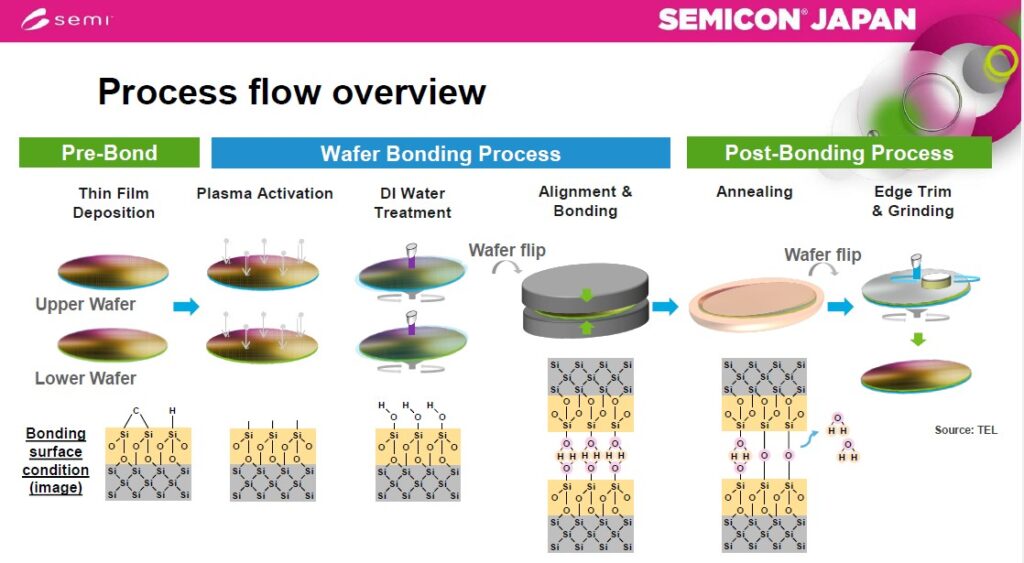

● Wafer Bonding の基本プロセス

- 表面酸化膜をラジカル化

- DI Water処理でOH基を形成

- OH基同士を水分子間力で貼り合わせ

- アニールでH₂Oを脱離しSiO₂結合へ

シンプルな原理だが、量産レベルでは高い均一性と欠陥抑制が求められる。

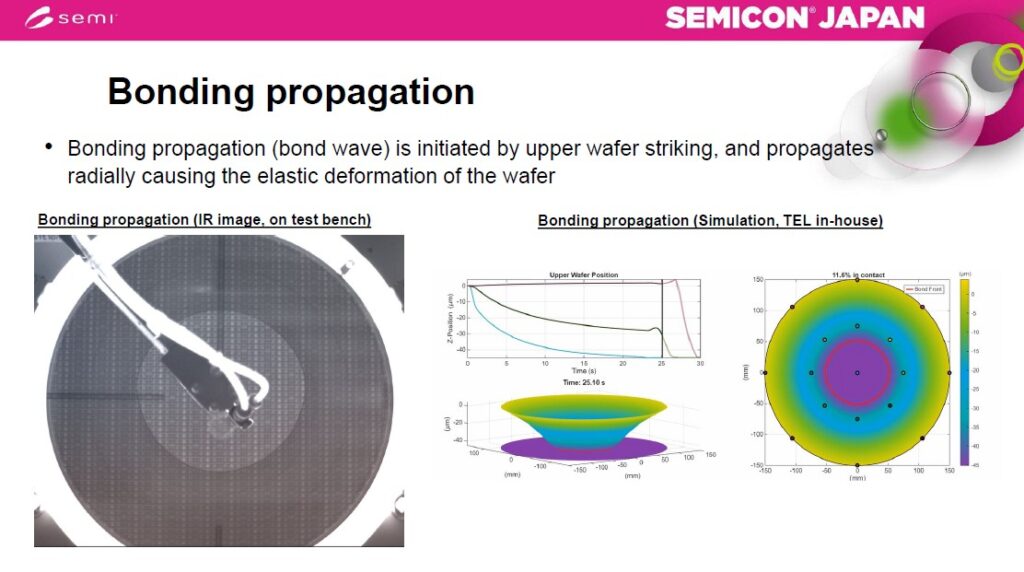

● Bonding Propagation(接合伝播)とは?

ウェーハ同士が貼り合わさる際、スマホの保護フィルムを貼るときのように 波(bond wave) が放射状に広がる。この波の速度や均一性は欠陥発生に直結するため、制御と予測が極めて重要だ。

- ハイブリッドボンディングや3D積層の歩留まりに直結

- CMOS 2.0 の裏面処理に不可欠

- シミュレーションと実測の整合性が工程最適化の鍵

3次元集積の裏側では、こうした“見えない物理現象”の理解と制御が進んでいる。

次世代DRAMを拓くOCTRAM(キオクシア 池田圭司氏)

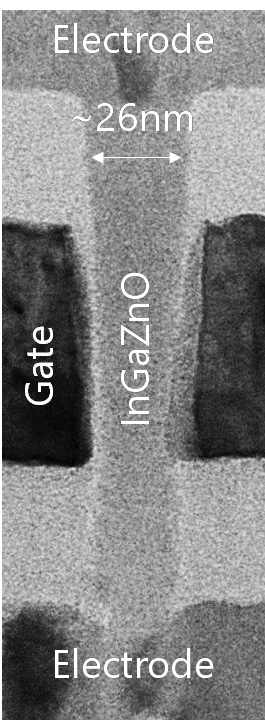

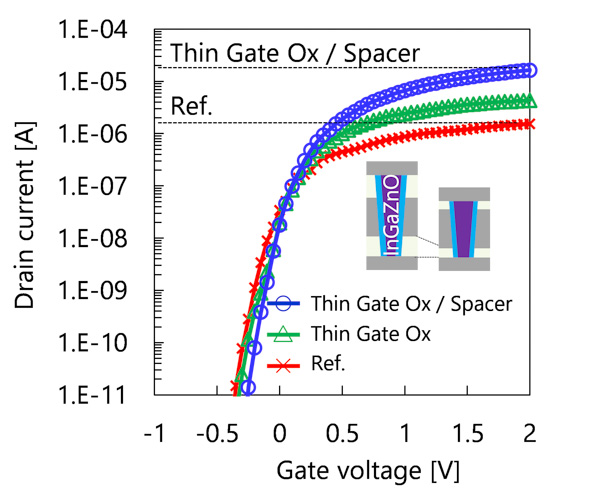

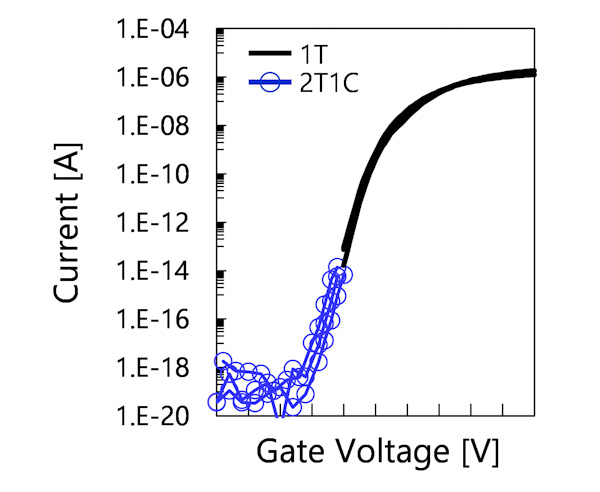

DRAMの微細化がSub10nmで限界に近づく中、キオクシアが提案するのが OCTRAM(Oxide-semiconductor Channel Transistor RAM) だ。InGaZnO(IGZO)をチャネル材料に用いることで、極低オフリーク電流や優れた電気特性を実現し、DRAMセルの立体構造化を可能にする。

● InGaZnO(IGZO)がもたらす革新

- 極低オフリーク電流

- ワイドバンドギャップによる高い電気特性

- 成膜プロセスによる立体構造化が可能

これにより、DRAMのさらなる高密度化と低消費電力化が期待される。

● 信頼性面での大きな利点

従来DRAMが抱える Variable Retention と Rowhammer の問題を、OCTRAMは構造的に回避できる。

- Variable Retention1

→ PN接合レスのためリテンションばらつきが小さい - Rowhammer2

→ 3D構造でWLがシールドとなり干渉を低減

(2D-NAND → 3D-NANDで干渉が減ったのと同じ理屈)

今後はセルピッチ、量産プロセス、大容量化が焦点となる。

※ InGaZnOは酸素欠損が伝導モデルであり、この酸素欠損は、BEOL(バックエンドプロセス)で水素の影響を受けやすいが、InGaZnOの組成比を最適化することでプロセスの影響を最小限に抑えてオン電流を最大化できるとのこと。

まとめ:3次元集積が半導体の未来を形づくる

SEMICON Japan 2025 の最終日は、

「微細化の限界を超えるための3次元化」

という明確な方向性が示された一日だった。

- ロジックは CMOS 2.0 へ

- 電源供給は BSPDN が本格化

- メモリは OCTRAM という新アーキテクチャへ

半導体は、もはや平面の世界では語れない。

3次元へ、そして異種統合へ。

その未来を支える技術が、確実に形になりつつあることを実感できるセッションだった。

コメント